используя синхронную логику создать счетчик в помехозащищенном коде грея с асинхронным сбросом

Язык описания аппаратуры Verilog HDL

Давайте подумаем, как на языке Verilog можно описать счетчик в коде Грея (Gray code). Такой счетчик может нам понадобиться для реализации асинхронного FIFO. В кодах Грея соседние значения меняются только в одном бите. Это делает возможным безопасную передачу последовательно меняющихся значений кодов из одного клокового домена в другой. Напомню, что в асинхронном FIFO указатели на голову/хвост очереди пересекают clock domain именно в кодах Грея.

Поскольку последовательность чисел в коде Грея нам известна (0,1,3,2,6,7,5. ), то первое, что приходит на ум – это написать вот такой код: module gray_cnt_v1(

input wire clk,

input wire nreset,

output reg [3:0]q

);

always @( posedge clk or negedge nreset)

if (

nreset)

q else

case (q)

4’b0000: q endcase

endmodule Это описание счетчика Грея вполне работоспособно, но оно далеко не самое удачное. Недостаток такого решения – его трудно написать и легко ошибиться при наборе этих двоичных чисел. Второе – код не параметризован. Что если придется писать, скажем, 64-х битный или 128-ми битный счетчик?

Мы знаем, что код Грея можно преобразовать в двоичный код с помощью «Исключающего ИЛИ». Так же и наоборот, двоичный код можно преобразовать в код Грея с использованием этой же операции и операции сдвига. Значит можно написать второй вариант «программы». Попробуем сделать обычный двоичный счетчик, и его выходные значения будем преобразовывать в код Грея:

module gray_cnt_v2(

input wire clk,

input wire nreset,

output wire [3:0]q

);

reg [3:0]bc; //bin counter

always @( posedge clk or negedge nreset)

if (

nreset)

bc else

bc //convert bin to gray

assign q = < bc[3], ^bc[3:2], ^bc[2:1], ^bc[1:0] >;

endmodule

Код стал компактнее, но стал ли он от этого лучше? Я бы сказал, что этот вариант даже хуже. В первом варианте gray_cnt_v1 на выходе нашего счетчика стоит регистр, фиксирующий выходное значение по фронту тактовой частоты. В этом легко убедиться, откомпилировав модуль в cреде Altera Quartus II и посмотрев результат в RTLViewer:

Во втором варианте gray_cnt_v2 выходы – это комбинационная логика, что очень плохо именно для счетчика Грея:

Мы не должны допускать формирование разных бит «счетчика» Грея в разное время, но именно это и может происходить в случае комбинационной логики на выходе нашего модуля, ведь путь формирования сигналов каждого из битов может оказаться разный.

При функциональной симуляции обоих модулей gray_cnt_v1 и gray_cnt_v2 мы увидим абсолютно одинаковый результат. Но это не значит, что все хорошо. Лучше отказаться от такого gray_cnt_v2 по указанной выше причине.

Следующий «правильный» метод может выглядеть не очень компактно, зато здесь все правильно:

module gray_cnt_v3(

input wire clk,

input wire nreset,

output wire [SIZE-1:0]q

);

parameter SIZE = 4;

integer i;

reg [SIZE-1:0]gray_cnt;

reg [SIZE-1:0]bin;

reg [SIZE-1:0]next_gray_cnt;

always @*

begin

//convert gray-to-bin

for (i=0; i >i);

//increment binary

bin=bin+1;

//convert bin-to-gray

next_gray_cnt = (bin>>1)^bin;

end

always @( posedge clk or negedge nreset)

if (

nreset)

gray_cnt else

gray_cnt assign q=gray_cnt;

По каждому клоку тактовой частоты записываем в регистр счетчика следующее предвычисленное значение next_gray_cnt. А вычисляем мы его в 3 этапа:

Откомпилируем теперь этот модуль в Altera Quartus II и посмотрим как выглядит все это в схематике RTLViewer:

Теперь можно просимулировать поведение счетчиков из примера 1 и 3. Напишем вот такой тестбенч на Verilog:

reg clk;

initial clk=0;

always

#10 clk=

reg nreset;

wire [3:0]cnt_value;

gray_cnt_v3 my_gray_cnt(

.clk(clk),

.nreset(nreset),

.q(cnt_value)

);

/*

gray_cnt_v1 my_gray_cnt(

.clk(clk),

.nreset(nreset),

.q(cnt_value)

);

*/

initial

begin

$dumpfile(«out.vcd»);

$dumpvars(-1, test);

nreset=0;

@( posedge clk); #0;

nreset=1;

Симулируем с помощью Icarus Verilog и смотрим как считает наш счетчик:

Русские Блоги

Verilog HDL синхронный сброс и асинхронный сброс (поворот)

содержание

1. Синхронный сброс

Аппаратная схема, синтезированная этим кодом, показана на рисунке ниже:

Синхронные схемы также обладают метастабильностью, но вероятность меньше, чем у схем асинхронного сброса.

Когда входной вывод Din находится на высоком уровне, а время снятия сигнала сброса находится в пределах Tsu и Th clk, последует метастабильное состояние. Как показано на временной диаграмме, когда время отмены сброса находится в clk Tsu с Th Внутри входные данные равны «1», а данные после прохождения и входные данные также находятся в Tsu и Th clk, поэтому это обязательно вызовет метастабильную ситуацию, аналогичную получению асинхронного сигнала;

2. Асинхронный сброс

Аппаратная схема, синтезированная этим кодом, показана на рисунке ниже:

3. Сравнение синхронного / асинхронного сброса

Преимущества синхронного сброса:

Недостатки синхронного сброса:

Преимущества асинхронного сброса:

Недостатки асинхронного сброса:

4. Асинхронный сброс и синхронный выпуск

Вышеуказанные недостатки могут быть устранены за счет использования асинхронного сброса и синхронного сброса. Так называемый асинхронный сброс, синхронное освобождение означает, что он не синхронизируется тактовым сигналом при поступлении сигнала сброса, но синхронизируется тактовым сигналом при высвобождении сигнала сброса.

Вообще говоря, синхронные системы используют асинхронный сброс. Это связано с тем, что реализация схемы синхронного сброса тратит больше ресурсов схемы, чем реализация схемы асинхронного сброса.

Сигнал сброса, который не был обработан с помощью «асинхронного сброса, синхронного освобождения» в тактовой области этого модуля. Когда он предоставляется этому модулю для асинхронного сброса, он должен быть » асинхронный сброс, синхронный выпуск ». Это обычное явление, когда два компонента в системе не находятся в одной и той же области часов.

В инженерной практике я действительно видел высокую вероятность того, что система выйдет из строя из-за процесса синхронизации без асинхронного сброса (объем сброса очень велик)

4.1. Принцип асинхронного сброса и синхронного сброса

Реализация кода Verilog:

Сигнал сброса, обрабатываемый функцией reset_gen, в процессе сброса асинхронного сброса, сигнал сброса непосредственно воздействует на терминал rst_sync_n, который играет роль асинхронного сброса;

Когда сигнал сброса высвобождается, вход триггера первого уровня равен Vcc, который равен 1. После следующего тактового импульса он синхронизируется с триггером второго уровня для достижения синхронизации освобождения;

Интеллектуальная рекомендация

Статическая и динамическая отправка в Java

Освойте команду jar

Упражнение «Think Python» 4-1: Пример схемы стека кода и размышления об остановке в этой главе

Глава 4 Пример: дизайн интерфейса Упражнение 4-1. Пример схемы стека кода в этой главе, точка остановки отклоняется от мышления 4.1 Упражнение 4.1.1】 Нарисуйте диаграмму стека, чтобы показать состояни.

Конвертировать PDF в SWF файл

1. Необходимо использовать службу pdf2swf.exe Во-вторых, код выглядит следующим образом.

Windows 10 Python 2.x совместим с Python 3.x

Некоторое время назад, из-за потребностей работы, Python 3.6.1, установленный на компьютере, использовал модуль M2Crypto для шифрования закрытого ключа, и дешифрование открытого ключа всегда происходи.

Дата: 21.05.2021 10:13

Оглавление

*О найденных опечатках и замечаниях просим сообщить admin@fpga-systems.ru

Доступно в PDF

Аннотация

1.0 Введение

2.0 Предназначение сброса

3.0 Общие примечания по стилю кодирования триггеров

4.0 Синхронный сброс

По мере проведения исследований для этой статьи был собран и рассмотрен сборник статей ESNUG и SOLV-IT. Около 80% собранных статей были посвящены вопросам синхронного сброса. Во многих статьях из SNUG утверждалось что-то вроде: “Мы все знаем, что лучший способ выполнить сброс в ASIC – это строго использовать синхронные сбросы”, или, возможно, “асинхронные сбросы плохи, и их следует избегать”. Тем не менее, было представлено мало доказательств, подтверждающих эти заявления. Использование синхронных или асинхронных сбросов имеет как преимущества, так и недостатки. Дизайнер / разработчик должен использовать подход, соответствующий определенному дизайну / проекту.

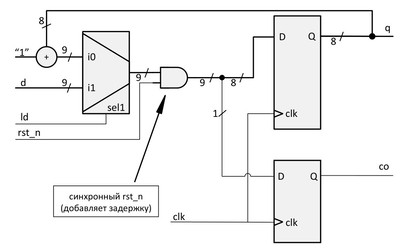

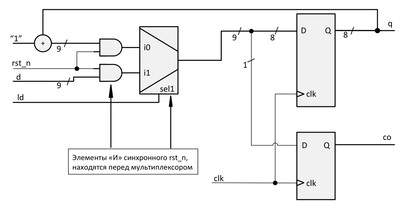

Синхронные сбросы основаны на предположении, что сигнал сброса будет влиять на состояние триггера (сбрасывать его) только при активном фронте тактового сигнала. Сброс может быть применен к триггеру как часть комбинационной логики, формирующей сигнал на D-входе триггера. Если это так, то стиль кодирования для описания сброса должен быть описан с помощью приоритетного if/else со сбросом в условии if и всей другой комбинационной логикой в ветке else. Если этот стиль не соблюдается строго, могут возникнуть две возможные проблемы. Во-первых, в некоторых симуляторах, основанных на логических уравнениях, логика может блокировать сброс и он не достигнет триггера. Однако, это проблема моделирования, а не аппаратная проблема, но помните, что одна из главных целей сброса – привести ASIC в известное состояние для выполнения моделирования. Во-вторых, сброс может “запаздывать” относительно тактового сигнала из-за высокого ветвления цепей сброса. Даже если сброс будет буферизован с помощью специального буфера (буфера сброса), разумно ограничить объем логики, которая должна быть сброшена. Этот стиль описания синхронного сброса можно использовать с любой логикой или библиотекой. В примере 3 показана реализация синхронного сброса как части счетчика с загрузкой данных с функцией переноса (carry out).

4.1 Стиль кодирования и пример схемы

Код Verilog в примере 4a и код VHDL в примере 4б показывают правильный способ описания триггеров с синхронным сбросом. Обратите внимание, что сброс не является частью списка чувствительности. Для Verilog исключение сброса из списка чувствительности – это то, что делает сброс синхронным. Для VHDL удаление сброса из списка чувствительности и проверка сброса после оператора “if clk’event и clk =» 1” делает сброс синхронным. Также обратите внимание, что сброс имеет приоритет над любым другим присвоением при использовании стиля кодирования «if-else.

Одна из проблем с синхронными сбросами заключается в том, что синтезатор не может просто взять и отличить сигнал сброса от любого другого сигнала данных. Рассмотрим код из примера 3, который приводит к схеме на рис. 3. В качестве альтернативы синтезатор мог бы создать схему, показанную на рис. 4.

1. Прим. пер.: подробнее про X-пессимизм:

Synopsys предоставляет директиву компилятора sync_set_reset, которая сообщает синтезатору, что данный сигнал является синхронным сбросом (или сигналом установки (set)). Синтезатор “подтянет” этот сигнал как можно ближе к триггеру, чтобы предотвратить возникновение этой проблемы. Директива может быть использована путем добавления следующей строки где-то внутри модуля:

// synopsys sync_set_reset «rst_n»

В общем, мы рекомендуем использовать атрибуты и директивы Synopsys только тогда, когда они необходимы и имеют значение; однако директива sync_set_reset не влияет на логическое поведение проекта, она влияет только на его функциональную реализацию. Опытный инженер предпочел бы избежать повторного синтеза на поздней стадии разработки проект и добавил бы директиву sync_set_reset ко всему RTL-коду на ранней стадии. Поскольку объявление ранее упомянутой директивы требуется только один раз, рекомендуется добавлять ее в каждый модуль с синхронными сбросами.

В качестве альтернативы решение можно использовать переменную синтеза hdlin_ff_always_sync_set_reset, значение которой следует установить в true, что даст тот же результат, не требуя вставки каких-либо директив в самом коде.

Несколько лет назад другой участник SNUG рекомендовал добавить переменную compile_preserve_sync_resets =» «true» [15]. Хотя эта переменная могла быть полезна несколько лет назад, она была удалена Synopsys, начиная с версии 3.4 b [38].

4.2 Преимущества синхронного сброса

Логика синхронного сброса будет синтезироваться в более компактные триггеры, особенно если сброс совмещается с логикой, генерирующей D-вход. Но в таком случае увеличивается число комбинационных логических элементов, поэтому общая экономия может быть не столь значительной. Однако, если дизайн микросхемы достаточно плотный, то экономия площади в один или два логических вентиля на триггер может повлиять на возможность размещения ASIC на подложке. Однако, при современных технологических нормах и больших размерах подложки экономия одного или двух логических вентилей на триггер, как правило, не играет важной роли и не будет существенным фактором того, уместится ли дизайн на подложке.

Использование синхронных сбросов обычно гарантирует, что схема на 100% синхронна.

Использование синхронных сбросов гарантирует, что сброс может произойти только на активном фронте тактового сигнала. Тактовый сигнал работает как фильтр при небольших глитчах сброса; однако, если эти сбои происходят вблизи активного фронта тактового сигнала, триггер может перейти в метастабильное состояние. Такое поведение ничем не отличается от любого другого ввода данных в триггер; любой сигнал, нарушающий требования по времени установления (setup), может привести к метастабильности.

В некоторых проектах сброс должен быть вызван набором внутренних условий. Для таких проектов рекомендуется использование синхронного сброса, поскольку он будет фильтровать глитчи, вызванные логикой формирования сброса (прим. пер. эффектом гонок в комбинационных схемах) между тактовыми сигналами

4.2 Недостатки синхронного сброса

Не все библиотеки ASIC имеют триггеры со встроенными синхронными сбросами. Однако, поскольку синхронный сброс – это просто еще один вход данных, вам действительно не нужен специальный триггер. Логика сброса может быть легко синтезирована вне самого триггера.

Для синхронных сбросов может потребоваться «удлинитель» импульсов, чтобы гарантировать достаточную длительность импульса сброса для обеспечения его наличия во время активного фронта тактового сигнала [16]. Это вопрос, который важно учитывать при работе с несколькими тактовыми доменами. Можно использовать небольшой счетчик, который будет обеспечивать достаточную длительность сигнала сброса.

Дизайнер должен уметь работать с проблемами симулятора. Потенциальная проблема существует, если сброс генерируется комбинационной логикой в ASIC или если сброс должен проходить через множество уровней локальной комбинационной логики. Во время моделирования, в зависимости от того, как генерируется сброс или как данные подаются на функциональный блок, сброс может быть замаскирован неопределенным состоянием X. Большое количество SNUG статей посвящено этому вопросу. Большинство симуляторов не смогут разрешить некоторые условия X-логики и, следовательно, заблокируют синхронный сброс [7] [8] [9] [10] [11] [12] [13] [14] [15] [34]. Обратите внимание, что это также может быть проблемой и с асинхронными сбросами. Проблема не столько в том, какой тип сброса вы используете, сколько в том, легко ли сигнал сброса управляется внешним выводом.

По своей природе синхронный сброс требует тактового сигнала для сброса схемы. Для одних проектов использование синхронного сброса является приемлемым, но для некоторых дизайнов может стать большой проблемой. Например, если у вас есть схема управления тактовой частотой, позволяющей включать и отключать тактовый сигнал для экономии энергопотребления (прим. пер. т.н. gated clock или clock gating), тактовый сигнал может быть отключен одновременно со сбросом. В этой ситуации будет работать только асинхронный сброс.

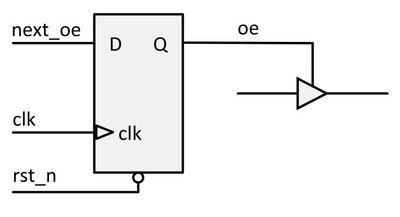

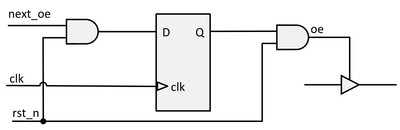

Требование к наличию тактового сигнала для осуществления сброса, является существенным, если ASIC/FPGA имеет внутреннюю tristate шину. Чтобы предотвратить конфликт на внутренней шине tristate при включении микросхемы, микросхема должна иметь асинхронный сброс питания (см. рис. 5). Можно использовать синхронный сброс, однако вы должны напрямую перевести сигнал разрешения tristate (сигнал ое) в неактивное состояние с помощью сигнала сброса (см. рис. 6). Этот синхронный метод имеет преимущество при более простом временном анализе для пути reset-to-HiZ.

Рисунок 5 – Асинхронный сброс для сигнала разрешения выхода

Рисунок 6 – Синхронный сброс для сигнала разрешения выхода

Русские Блоги

Синхронный сброс и асинхронный сброс

Краткое введение

Прежде чем выбрать стратегию сброса в реальном проекте, необходимо рассмотреть многие вопросы проектирования, такие как использованиеСинхронный сбросилиАсинхронный сбросилиАсинхронный сброс и синхронный выпуск(Асинхронный сброс синхронного выпуска или синхронный асинхронный сброс), а также необходимость сброса каждого триггера.Основная цель сброса состоит в том, чтобы заставить устройство войти в определенное состояние, которое может работать стабильно, что не позволяет устройству переходить в случайное состояние после включения и вызывать его разрядку., В реальном процессе проектирования проектировщик должен выбрать наиболее подходящий метод сброса для самого проекта;

Синхронный сброс

Синхронный сброс означает, что сигнал сброса действителен только при наступлении переднего фронта часов. Код синхронного сброса RTL:

Интегрированная диаграмма RTL выглядит следующим образом:

Асинхронный сброс

Асинхронный сброс означает, что независимо от того, наступает ли фронт такта, пока сигнал сброса действителен, система сбрасывается. RTL код асинхронного сброса:

Интегрированная диаграмма RTL выглядит следующим образом:

Сравнивая представление RTL после их синтеза, было обнаружено, что для синхронного сброса будет использоваться больше логических блоков, поскольку обычные триггеры имеют терминалы асинхронного сброса;

Преимущества и недостатки синхронного сброса и асинхронного сброса

Преимущества синхронного сброса:

Недостатки синхронного сброса:

Преимущества асинхронного сброса:

Недостатки асинхронного сброса:

Асинхронный сброс и синхронный выпуск

То есть сигнал сброса синхронизируется с входным сигналом через двухступенчатый синхронизатор, а код выглядит следующим образом:

Язык описания аппаратуры Verilog HDL

В этой статье я постараюсь рассказать про счетчики, про их описание на Verilog и их схемотехническое представление в RTLViever.

Счетчики широко применяются везде, где нужно посчитать число некоторых событий, да и не только для этого

Двоичный счетчик.

reg [3:0]counter;

always @( posedge clk)

counter

Вот представление этого счетчика в RTLViewer:

Двоичный счетчик с асинхронным сбросом.

reg [3:0]counter;

always @( posedge clk or posedge reset)

if (reset)

counter else

counter

Вот его схемотехническое представление в RTLViewer:

И вот его временная диаграмма:

Видно, что по фронту тактовой частоты в регистры счетчика будет записываться очередное значение, на единицу большее, чем предыдущее. Если в коде Verilog использовать минус, вместо плюса, то счетчик будет считать в обратную сторону.

Еще раз подчеркну, что ассинхронный сброс или установка как правило используются только в самом начале работы устройства.

Двоичный счетчик с синхронным сбросом.

Здесь обнуление регистров счетчика происходит по фронту тактовой частоты. В схеме появляется мультиплексор, который выбирает для записи в регистры счетчика либо следующее значение, либо ноль.

always @( posedge clk)

if (reset)

counter else

counter

Вот представление в RTL:

И его временная диаграмма:

Счетчик с асинхронным сбросом и входом разрешения и сигналом загрузки.

Чтобы как-то разнообразить описание счетчиков я решил в этом примере дать более «осмысленные» имена сигналам. Представим себе, что мы разрабатываем свой процессор:

Вот так это все может быть записано на Verilog:

always @( posedge clk or posedge reset)

begin

if (reset)

instr_ptr else

if (

cpu_wait)

begin

if (branch_cond)

instr_ptr else

instr_ptr end

end

Давайте рассмотрим, что представляет из себя этот код в RTLViewer:

А вот временная диаграмма:

На этой диаграмме, как пример, видно такт ожидания на инструкции процессора по адресу 3 и переход с адреса 6 на адрес 35.

Еще счетчики могут быть не только двоичными. Вот, например:

Счетчик по модулю 10.

Понятно, что аналогично можно строить счетчики по любому модулю.

wire cout;

reg [3:0]counter;

always @( posedge clk or posedge reset)

begin

if (reset)

counter else

if (counter==4’d9)

counter else

counter end

assign cout = (counter==4’d9);

Считает эта схема вот так:

Сигнал cout удобно использовать, например, для каскадного соединения счетчиков как сигнал разрешения счета для старших десятичных разрядов.

В следующей статье я хотел рассказать про сдвиговые регистры.