узел эвм предназначенный для арифметического сложения кодов

Узел арифметического устройства ЭВМ, осуществляющий операцию суммирования чисел

Последняя бука буква «р»

Ответ на вопрос «Узел арифметического устройства ЭВМ, осуществляющий операцию суммирования чисел «, 8 (восемь) букв:

сумматор

Альтернативные вопросы в кроссвордах для слова сумматор

Определение слова сумматор в словарях

Энциклопедический словарь, 1998 г. Значение слова в словаре Энциклопедический словарь, 1998 г.

узел арифметического устройства ЭВМ, осуществляющий операцию суммирования чисел. Выполняется на логических элементах, интегральных схемах.

Большая Советская Энциклопедия Значение слова в словаре Большая Советская Энциклопедия

(от позднелат. surnmo ≈ складываю, от лат. summa ≈ сумма, итог), основной узел арифметического устройства ЦВМ, посредством которого осуществляется операция сложения чисел. При поразрядном сложении десятичных чисел (например, 157, 68 и 9) складывают сначала.

Примеры употребления слова сумматор в литературе.

В процессоре имеются два устройства целочисленной арифметики, а также умножитель и сумматор чисел с плавающей запятой.

Аппаратура процессора состоит из 32-разрядного арифметически-логического устройства, группового сдвигателя, умножителя Бута, сумматора адресов и регистрового файла из 25 регистров, позволяющего за один такт прочитать два и записать один регистр.

Не получалось и более простое: импульсы, поданные с усилителя на сумматор, ничего не давали, и вскоре Крэл распорядился придвинуть павильончик с пультом почти вплотную к башне.

Отведения на сумматор были сделаны, и на расстоянии двенадцати метров от башни, в наскоро построенном, но хорошо оборудованном павильончике был установлен пульт.

Источник: библиотека Максима Мошкова

Сумматоры

Сумматором называется узел ЭВМ, предназначенный для арифметического сложения кодов. Сумматоры в зависимости от используемых логических схем различаются на комбинационные и накапливающие. Комбинационный сумматор представляет собой комбинационную схему, которая формирует суммы слагаемых, подаваемых одновременно на входы схемы, и не имеет в своем составе элементов памяти. Накапливающие сумматоры имеют память, в которой накапливают результаты суммирования.

По числу входов различают полусумматоры, одно и многоразрядные ( параллельные) сумматоры. В зависимости от того, как организованы межразрядные переносы, сумматоры делятся на сумматоры с последовательным, параллельным и групповыми переносами. В зависимости от системы счисления, сумматоры бывают двоичные, десятичные и прочие.

Основу всех сумматоров составляют одноразрядные сумматоры. Причем, сложение n-разрядных чисел осуществляется с помощью n одноразрядных сумматоров коммутацией цепей их переноса.

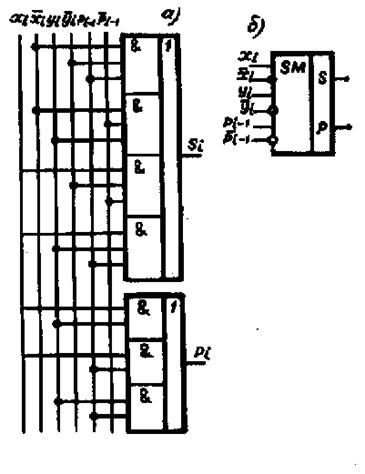

Одноразрядные сумматоры. Одноразрядные сумматоры предназначены для сложения одноименных разрядов двух слагаемых (хi и уi) с учетом переноса из предыдущего разряда (Рi-1) и вырабатывают в том же машинном такте значения суммы (Si) и переноса в следующий разряд (Pi). Другими словами одноразрядный сумматор складывает три бита xi, yi и Рi-1 и формирует Si и Рi.

Сумматоры, в которых при сложении двух слагаемых (х и у) не учитывается перенос из младшего разряда, называют полусумматорами. Полусумматор имеет два входа (xi и yi) и два выхода Рi и Si. Таблица истинности полусумматора может быть записана в виде табл. 4.1., по которой записываются логические функции Si и Pi:

| xi | yi | si | pi | n/n | xi | yi | pi-1 | si | pi |

|

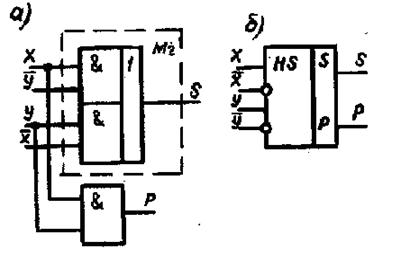

На рис. 4.9 показана схема полусумматора и его обозначение на функциональных схемах.

Рис. 4.9. Схема полусумматора

Таблицу истинности одноразрядного сумматора приведена в таблице 4.1.

Схема одноразрядного полного сумматора показана на рис. 4.10.

Рис. 4.10. Одноразрядный полный сумматор

Многоразрядные сумматоры.

В зависимости от того, как обрабатываются (суммируются) разряды n-разрядных чисел, различают многоразрядные сумматоры последовательного и параллельного действия.

В многоразрядных сумматорах параллельного действия разряды слагаемых обрабатываются параллельно. Количество сумматоров в них соответствует разрядности обрабатываемых чисел. По способу реализации цепей переноса сумматоры параллельного действия могут иметь следующую организацию: сумматоры с последовательным, одновременным и групповым переносом.

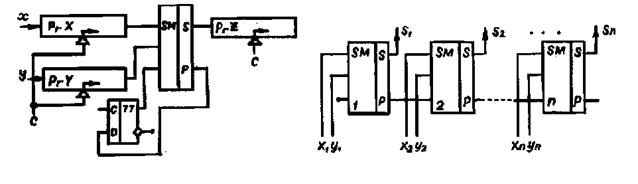

В сумматорах параллельного действия (рис. 4.12) с одновременным переносом сигнал переноса вырабатывается одновременно во всех разрядах. Рассмотрим синтез схем одновременного формирования переносов в 4-х разрядных сумматорах.

Рис. 4.11. Последовательный сумматор Рис. 4.12. Паралельный сумматор

Параллельные сумматоры с групповыми переносами, где переносы внутри групп формируются одновременно, а между группами последовательно, называют сумматорами с цепными переносами.

Узлы ЭВМ

Узлом ЭВМ называется совокупность функционально связанных элементов, предназначенных для выполнения определенных операций над двоичными словами. Узлы ЭВМ являются основными элементами реализации аппаратных функций ЭВМ (преобразование, передача, хранение и управление информацией). Они также обеспечивают преобразование кодов, счет импульсов, сравнение кодов, сдвиг информации.

По выполняемым функциям узлы делятся на регистры, сумматоры (накапливающего типа), счетчики, дешифраторы, шифраторы, мультиплексоры, демультиплексоры, схемы сравнения кодов, программируемые логические матрицы (ПЛМ), аналого-цифровые и цифроаналоговые преобразователи (АЦП и ЦАП) и пр.

Регистр — узел ЭВМ, предназначенный для хранения двоичных слов и выполнения над ними некоторых логических операций. Регистр представляет собой совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных схем, обеспечивающих выполнение некоторых операций, таких как:

По способу приема и выдачи информации регистры делятся на:

Параллельные регистры. Используются для выполнения операций приема, хранения, выдачи и поразрядных логических операций над словами и представляют собой совокупность /??-, /)- и Г-триггеров, имеющих связанные входные и выходные цепи (рис. 1.20).

Рис. 1.20. Параллельный регистр:

ПЧ — прием числа; СБ — сброс регистра в 0; ВПК — выдача прямого кода;

ВОК — выдача обратного кода

Сдвиговые регистры. Используются для выполнения следующих операций:

Самая простая схема сдвигового регистра строится на /)-триг-герах и имеет вид, приведенный на рис. 1.21.

Рис. 1.21. Простейший сдвиговый регистр

Прямой выход 0, предыдущего разряда поступает на информационный вход й последующего разряда. Благодаря этому каждый синхросигнал устанавливает последующий триггер в состояние, в котором до этого находился предыдущий разряд, осуществляя тем самым сдвиг информации на разряд влево (или вправо).

Реверсивные регистры сдвига. Обеспечивают возможность сдвига информации как влево, так и вправо (рис. 1.22).

Если сигнал на шине N равен «1», то потенциал на входе /) /-го триггера определяется выходом 0,_, триггера, стоящего слева от него (/’- 1). Если сигнал равен «О», то потенциал на входе /)

Счетчик с последовательным переносом. Строится на основе Г-триггеров (рис. 1.23).

Здесь /рсг = /7тт, где п — разрядность счетчика, тт — время переключения триггера. Чем больше разрядность слова, тем больше

время регистрации, поэтому счетчик имеет наиболее низкое быстродействие.

Вентиль сквозного переноса

Рис. 1.24. Счетчик со сквозным переносом

Счетчик с параллельным переносом имеет максимальное быстродействие. Здесь Грег = тт + ти.

Счетчик с групповым переносом. Из-за конечности коэффициентов объединения элементов «И» число разрядов в счетчике с параллельным переносом не может быть очень большим (обычно не более 8 разрядов). Если же требуется больше разрядов, то целесообразно использовать групповой перенос, при котором переносы внутри группы формируются параллельно, а между группами — или последовательно, или параллельно.

Вычитающий счетчик. Строится по принципу суммирующего счетчика, только подача сигналов осуществляется с инверсных выходов предыдущих разрядов.

Реверсивный счетчик. В зависимости от наличия сигнала сложения или вычитания ведет счет в прямом или обратном направлениях.

Счетчик с предустановкой. Используется, например, в качестве счетчика команд (СчАК) — см. рис. 3.1. Позволяет вначале переслать некоторый код в счетчик, а затем продолжить прерванный счет, начиная с этого кода, записанного в счетчике.

Пересчетная схема. Отличается от счетчиков способом снятия результата. В счетчиках показания снимаются в параллельном коде. В пересчетных схемах единичный сигнал формируется на выходе после подачи определенного количества импульсов на входе.

Сумматор — узел ЭВМ, выполняющий суммирование двоичных кодов чисел. Он является узлом преобразования информации. Различают комбинационные и накапливающие сумматоры.

В комбинационных сумматорах оба слагаемых подаются одновременно. При этом на выходах сумматоров фиксируется сумма, которая существует до тех пор, пока на входах действуют слагаемые.

В накапливающих сумматорах вначале подается 1-е слагаемое, которое запоминается сумматором. После подачи 2-го слагаемого в сумматоре образуется сумма, которая тоже запоминается.

В зависимости от способов обработки разрядов слагаемых различают сумматоры:

В зависимости от способа реализации переносов различают сумматоры:

Многоразрядные сумматоры строятся как совокупность одноразрядных (см. рис. 1.19).

АРИФМЕТИ́ЧЕСКОЕ УСТРО́ЙСТВО

Скопировать библиографическую ссылку:

АРИФМЕТИ́ЧЕСКОЕ УСТРО́ЙСТВО (АУ), одно из осн. устройств ЭВМ, входящее в состав процессора, в котором выполняются арифметич. и логич. операции, т. е. происходит собственно преобразование информации. Различают АУ универсальные и специализированные. Универсальное АУ выполняет такие операции, как сложение, вычитание, сравнение, преобразование, умножение, деление, вычисление квадратного корня, сдвиг и др., предусмотренные системой команд ЭВМ. Простейший вид универсального АУ – арифметико-логическое устройство (АЛУ). Оно обрабатывает числа с фиксированной запятой (целые числа), выполняет операции сложения, вычитания, сдвига и логич. операции. Специализир. АУ выполняет группу близких по алгоритму операций. Так, устройство сложения реализует операции сложения, вычитания, сравнения и преобразования типов и форматов данных; устройство деления – деление и вычисление квадратного корня. Универсальное АУ имеет меньший объём оборудования, чем неск. специализированных, совместно выполняющих такие же функции. Преимуществом специализир. АУ является меньшее время выполнения операции. В состав АУ входят регистры, сумматоры, коммутаторы, сдвигатели, кодировщики приоритетов, дешифраторы и др. узлы. Регистры предназначены для врем. хранения информации, а сумматоры, сдвигатели и др. – для преобразования информации. Скорость работы этих узлов, особенно сумматора, в значит. степени определяет быстродействие АУ. Для работы АУ необходимо получить код операции и операнды (числа, над которыми выполняется операция). В вычислит. машинах существуют две формы представления чисел: с фиксированной запятой (преим. для целых чисел) и с плавающей запятой. Для представления целых чисел в ЭВМ обычно применяют 8-, 16-, 32- и 64-разрядные форматы, а для вещественных – 32-, 64-, 80- и 128-разрядные.

Учебно-методический комплекс

По предмету «Архитектура аппаратных средств»

Тема 2.1. Логические основы ЭВМ, элементы и узлы

Базовые логические операции и схемы: конъюнкция, дизъюнкция, отрицание. Таблицы истинности. Схемные логические элементы: регистры, триггеры, сумматоры, мультиплексор, демультиплексор, шифратор, дешифратор, компаратор. Принципы работы, таблица истинности, логические выражения, схема.

Каждая логическая связка рассматривается как операция над логическими высказываниями и имеет свое название и обозначение:

НЕ- Операция, выражаемая словом «не», называется отрицанием и обозначается чертой над высказыванием (или знаком). Высказывание истинно, когда A ложно, и ложно, когда A истинно. Пример. «Луна — спутник Земли» (А); «Луна — не спутник Земли» ( A ).

ИЛИ Операция, выражаемая связкой «или» (в неисключающем смысле этого слова), называется дизъюнкцией (лат. disjunctio — разделение) или логическим сложением и обозначается знаком v (или плюсом). Высказывание А v В ложно тогда и только тогда, когда оба высказывания А и В ложны. Например, высказывание «10 не делится на 2 или 5 не больше 3» ложно, а высказывания «10 делится на 2 или 5 больше 3», «10 делится на 2 или 5 не больше 3», «10 не делится на 2 или 5 больше 3» —истинны.

Для логического элемента «И» выход Q будет содержать лог.1, только если на оба входа («А» и «В») будет подан сигнал лог.1

Выход Q, элемента «ИЛИ», будет иметь лог.1, если на любой из двух входов или же на оба входа сразу подать лог.1

В данном случае выход Q, логического элемента «НЕ», будет иметь сигнал противоположный входному сигналу.

На выходе Q элемента «И-НЕ» будет лог.1 если на обоих входах одновременно отсутствует сигнал лог.1

Только если на оба входа логического элемента «ИЛИ-НЕ» подать лог.0 мы получим на его выходе Q сигнал соответствующий лог.1

Элемент «Исключающее ИЛИ»

В данном случае выход Q будет содержать лог.1, если на вход элемента «Исключающее ИЛИ» поданы два противоположных друг другу сигнала.

Подведем итог, собрав все полученные ранее результаты работы логических элементов в единую таблицу истинности:

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

Регистрами называют устройства, предназначенные для приема, хранения и передачи информации. Последняя в регистре хранится в виде двоичного кода, каждому разряду которого соответствует свой элемент памяти (разряд регистра), выполненный на основе триггеров RS-, JK-, или D-типа.

Классификацию регистров можно провести по различным признакам, важнейшими из которых являются способ ввода-вывода информации и характер представления вводимой и выводимой информации.

Сумматором называется узел ЭВМ, предназначенный для арифметического сложения кодов. Сумматоры в зависимости от используемых логических схем различаются на комбинационные и накапливающие. Комбинационный сумматор представляет собой комбинационную схему, которая формирует суммы слагаемых, подаваемых одновременно на входы схемы, и не имеет в своем составе элементов памяти. Накапливающие сумматоры имеют память, в которой накапливают результаты суммирования.

По числу входов различают полусумматоры, одно и многоразрядные ( параллельные) сумматоры. В зависимости от того, как организованы межразрядные переносы, сумматоры делятся на сумматоры с последовательным, параллельным и групповыми переносами. В зависимости от системы счисления, сумматоры бывают двоичные, десятичные и прочие.

Основу всех сумматоров составляют одноразрядные сумматоры. Причем, сложение n-разрядных чисел осуществляется с помощью n одноразрядных сумматоров коммутацией цепей их переноса.

Обычно в качестве демультиплексора используют дешифраторы двоичного кода в позиционный, в которых вводят дополнительный вход стробирования.

Из-за сходства схем мультиплексора и демультиплексора в КМОП сериях есть микросхемы, которые одновременно являются мультиплексором и демультиплексором, смотря с какой стороны подавать сигналы.

Например, К561КП1, работающая как переключатель 8х1 и переключатель 1х8 (то есть, как мультиплексор и демультиплексор с восемью входами или выходами). Кроме того, в КМОП микросхемах помимо переключения цифровых сигналов (логических 0 или 1) существует возможность переключения аналоговых.

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением п = 2т, где п — число входов, т — число выходов.

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением т = 2n, где п — число входов, а т — число выходов.

iуi+xi

iуi+xi i; (4.1) Pi=xiуi

i; (4.1) Pi=xiуi